Project Overview

What is Digital ASIC fabrication in this context?

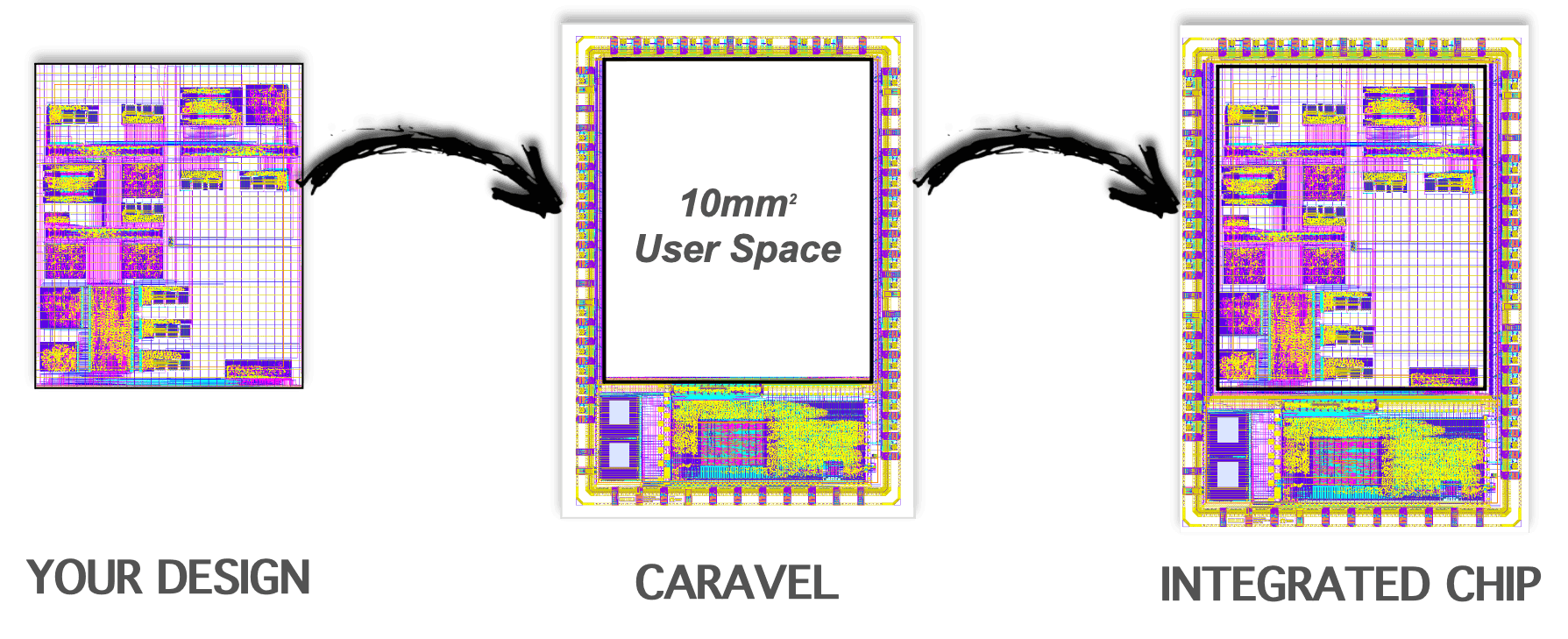

Our project "Digital ASIC Fabrication" involves the creation of a Application Specific Integrated Ciruit using the efabless workflow as a baseline constraint. The efabless workflow means that our design is integrated into the "Caravel" SoC, specifically inside of the "User Space". Our design is then extensively tested in the efabless "precheck" process to ensure the chip is not "dead on arrivial", and our own testing process to ensure functionality when it is printed/made physically, once it finally passes precheck and our own checks it's then sent off to efabless for physical creation.

What is our User Space project?

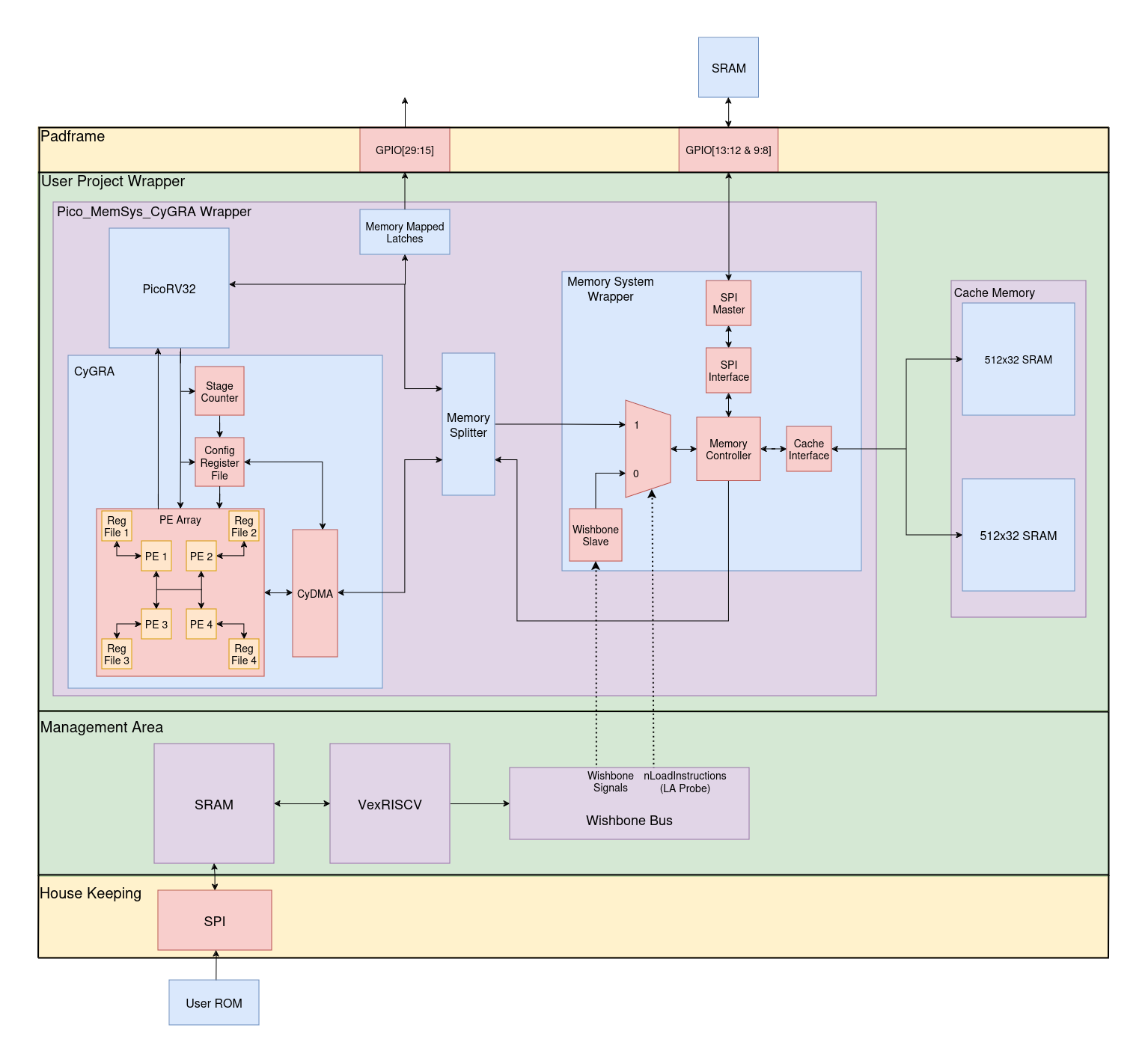

The overall goal of our project is to recreate a "Reprogrammable ISA" that involves the creation of a RISC-v processor based on an existing IP, placing it within the userspace and adding a custom logic unit (CGRA-like construction) in parallel which will be muxed based on if we're running a custom instruction.

Some Specifics

- RISC-v Processor is based on the picorv32 implementation: picorv32 - Written in Verilog

- Functions as a normal RISC-v processor when not executing custom instructions

Where can I find out more?

More information and specifics about our project can be found in our design document(s) linked below, also you can check out our official project repository above (fall), or our new repository here. If you are a future senior design group or a student looking for more information you may look for more information from ChipForge or Dr. Duwe.

Current Progress

Prep Phase

✅

Our prep phase consisted of learning the efabless tools by completing chipforge tutorials and reading caravel documentation. Additionally we set up vms to act as our shared workspace to boost productivity and ensure there was no mismatch in system setups. Finally we chose our high level goal of the project, our Reprogrammable ISA.

November Chip

✅

The November chip stage consisted of implementing the CprE 3810 Lab 2 project using the efabless workflow to prove that we'd learned this tools and were comfortable with the entire process of creating a design, validating, hardening, and passing pre-check. Additionally we worked with sddec24-12 to have this mini-project implemented with their project (more info at their page).

Picorv32 baseline

✅

The picorv32 baseline phase consisted of finalizing our IP choice for the baseline RISC-v processor in the user area that will be extended upon. We had a decision matrix for this process and chose the picorv32 as it is size optimized and easily extensible, and uses verilog. This additionally consisted of creating a high-level design of our project and visualizing all individual necessary components. We got the picorv32 to harden and function using efabless tools.

Accelerator Design

✅

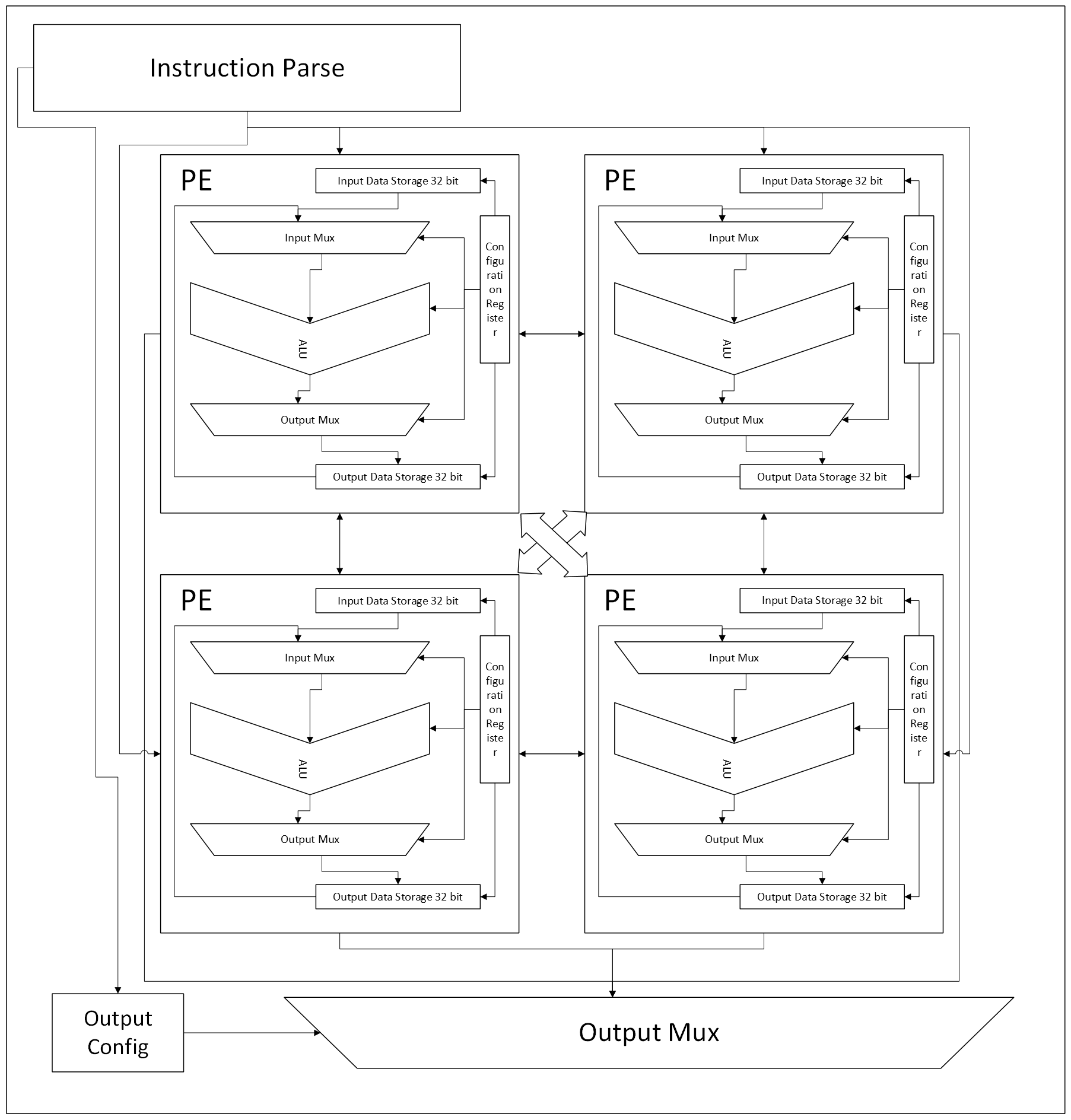

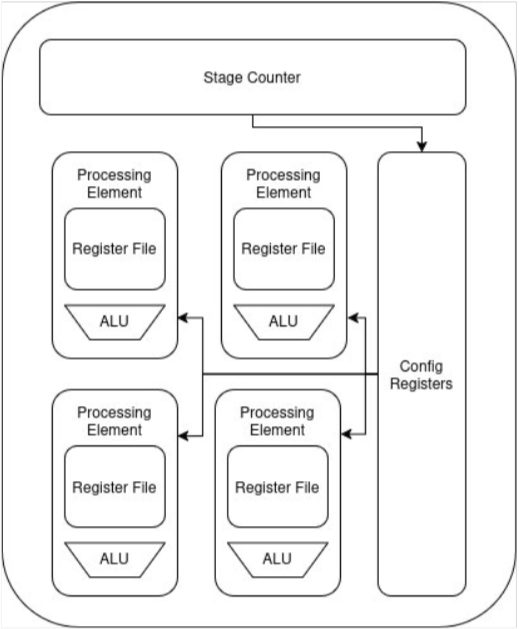

Our initial accelerator design consists around picking processes to accelerate and then designing an accelerator for that task, as of right now (12/07/2024) we're considering tasks such as FFT, Encoding/Decoding, and accelerating the Math.h library. Additionally we've come up with an initial design for math.h that we're dubbing the "CyGRA" (CGRA 1.0) pictured below, and below that is the diagram of our CyGRA 3.0

Integration

✅

The integration phase will consist of the design, implementation, and integration of additional components needed for the accelerator and picorv32 processor, and the implementation of memory interfaces that will be connecting individual modules. There will be verilog unit tests, and FPGA system tests to ensure functionality. So far our additional components consists of; Interrupt Module, SPI unit, Memory controller, Wishbone Slave.

Testing & Precheck

✅

Unfortunately efabless has seised operations due to a lack of funding, with our extra time we have decided to overhaul our CyGRA into a CyGRA 2.0 model and work towards a new deadline of May 2nd. Even though our project is currently up in air about being fabricated we're still working towards getting a working/tested project to leave to Dr. Duwe and ChipForge, we hope our project serves a good reference for a non-trivial digital ASIC fabrication design.

Team Members

Camden Fergen

DevOps, Project LeadSoftware Engineering Major with from Ames, IA, with a focus on Embedded Systems

John Huaracha

Testing lead

Computer Engineering major from Elgin, IL, with a focus on RTL design

Nicholas Lynch

Harden & Verification lead

Computer Engineering major from Aurora, IL, with a focus on computer hardware design

Calvin Smith

Accelerator Design lead

Computer Engineering major from Cedar Rapids, IA, with a focus on RTL design

Levi Wenck

Comm. Interfaces lead

Computer Engineering major from Iowa City, IA, with a focus on RTL design

Weekly Reports

Fall

Report 1Report 2

Report 3

Report 4

Report 5

Report 6

Report 7

Report 8

Report 9

Report 10

Spring

Report 1Report 2

Report 3

Report 4

Report 5

Report 6

Lightning Talks

Product ResearchProblem & Users

User needs & Reqs

Project Planning

Detailed Design

Contextualization

Prototyping

Design Documents

Design Doc WinterDesign Doc Spring Final

Presentations

Design Panel PresentationIRP Presentation

Final Poster