# **Digital ASIC Fabrication**

**Design Document**

sdmay25-28

Client & Faculty Advisor: Dr. Henry Duwe

Camden Fergen

John Huaracha

Nicholas Lynch

Calvin Smith

Levi Wenck

sdmay25-28@iastate.edu

sdmay25-28.sd.ece.iastate.edu

Revised: May 3<sup>rd</sup>, 2025

Version 1.5

# **Executive Summary**

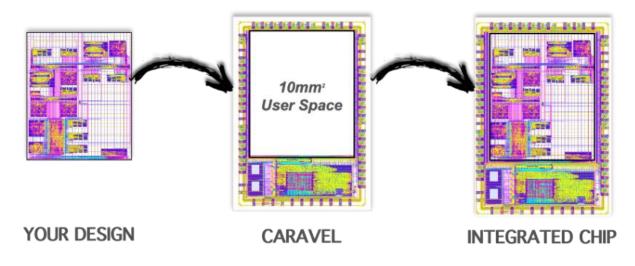

There are not many ways for students to experience, learn, and participate in Digital ASIC design. Thankfully, due to the introduction of open-source tools and designs such as Caravel Harness and OpenLANE, ASIC design is achievable for undergraduate students. Our project will be leveraging these tools to make a digital ASIC of our own. We aim to create an open-source coarse-grained reconfigurable architecture named the CyGRA, attached to an open-source microcontroller. We hope our project can help students learn about Computer Hardware and Digital IC design by providing a hands-on digital IC that students can experiment with and learn from. We also hope our project can also serve as a jumpstart point for new students who may want to try digital IC design.

To complete our project, we are utilizing the open-source tools and designs from Efabless. We are using a CGRA co-processor integrated into a microcontroller to extend an open-source ISA. There have been a handful of decisions made for our design: We have chosen to use the PicoRV32 as our microcontroller core, DFFRAM for on-chip memory, as well as a cache system to extend the memory size and utilize off-chip memory. The goal for our CyGRA co-processor is to accelerate certain instructions, as well as allow users to define their own configurations to potentially accelerate their own instructions. We also have experience with the open-source tooling provided by Efabless, so in the event an opportunity arises we can get our chip fabricated.

Update: As of March 2<sup>nd</sup>, 2025, Efabless has shutdown. Because of this, we currently do not have a plan for getting the chip fabricated. Regarding our senior design project, this has little change in terms of our project design, and we will continue to use the Efabless tooling, but we no longer have any access to tech support from Efabless in the event we run into issues. Additionally, we now no longer need to have the project ready for Efabless's April 21st deadline, which will allow us more time to design and test our system

# Learning Summary

### Development Standards & Practices Used

IEEE 1754-1994: IEEE Standard for a 32-bit Microprocessor Architecture

#### IEEE 1364-2001: IEEE Standard Verilog Hardware Description Language

#### IEEE 1364.1-2002: IEEE Standard for Verilog Register Transfer Level Synthesis

#### Summary of Requirements

- Project must be compatible with the Skywater 130nm process

- Entire project must be open source

- Function as a microcontroller when provided with standard instructions

- Support custom instructions defined by the user

- Stores and runs programs provided by the user

- HDL used is Verilog

### Applicable Courses from Iowa State University Curriculum

- CPRE 2810 Digital Logic

- CPRE 2880 Embedded Systems

- CPRE 3810 Computer Organization and Assembly Level Programming

- CPRE 4870 Hardware Design for Machine Learning

- CPRE 4880 Embedded Systems Design

- EE/CPRE 3300 Integrated Electronics

- EE/CPRE 4650 Digital VLSI Design

#### New Skills/Knowledge acquired that was not taught in courses

Skills:

- ASIC Chip Design

- Chip Fabrication

- Memory system

- Reconfigurable architecture

- Using open-source tools

Tools:

- Caravel Harness

- CocoTB

- Magic DRC

- Netgen LVS

- OpenLANE/OpenROAD

| Executive Summary                                             | 2  |

|---------------------------------------------------------------|----|

| Learning Summary                                              | 3  |

| Development Standards & Practices Used                        | 3  |

| Summary of Requirements                                       | 3  |

| Applicable Courses from Iowa State University Curriculum      | 3  |

| New Skills/Knowledge acquired that was not taught in courses  | 3  |

| Table of Contents                                             | 6  |

| List of Symbols and Definitions                               | 7  |

| Introduction                                                  | 8  |

| Problem Statement                                             | 8  |

| Intended Users                                                | 9  |

| Chip Forge Club Member                                        | 9  |

| Hardware Students                                             | 9  |

| Professors                                                    | 9  |

| Requirements, Constraints, And Standards                      | 9  |

| Requirements & Constraints                                    | 9  |

| Engineering Standards                                         |    |

| Project Plan                                                  | 12 |

| Project Management/Tracking Procedures                        | 12 |

| Task Decomposition                                            | 12 |

| Project Proposed Milestones, Metrics, and Evaluation Criteria | 13 |

| Project Timeline/Schedule                                     | 14 |

| Risks and Risk Management/Mitigation                          |    |

| Personnel Effort Requirements                                 | 17 |

| Other Resource Requirements                                   |    |

| Design                                               |

|------------------------------------------------------|

| Design Context                                       |

| Broader Context                                      |

| Prior Work/Solutions19                               |

| Technical Complexity21                               |

| Design Exploration                                   |

| Design Decisions21                                   |

| Ideation                                             |

| Decision-Making and Trade-Off22                      |

| Final Design24                                       |

| Overview                                             |

| Detailed Design and Visuals26                        |

| Functionality                                        |

| Areas of Challenge                                   |

| Technology Considerations31                          |

| Testing                                              |

| Unit Testing                                         |

| Interface Testing                                    |

| Integration Testing                                  |

| System Testing                                       |

| Regression Testing                                   |

| Acceptance Testing34                                 |

| Results                                              |

| Implementation                                       |

| Design Analysis                                      |

| Ethics and Professional Responsibility               |

| Areas of Professional Responsibility/Codes of Ethics |

| Four Principles                                      |

| Virtues                                              |

| Closing Material                              | 2 |

|-----------------------------------------------|---|

| Summary of Progress                           | 2 |

| Value Provided42                              | 2 |

| Next Steps43                                  | 3 |

| References                                    | 4 |

| Appendices4                                   | 5 |

| Operation Manual                              | 5 |

| Alternative/Initial Version of Design         | 5 |

| Relevant code                                 | 6 |

| Team                                          | 6 |

| Team Members40                                | 6 |

| Required Skills Sets                          | 6 |

| Skills Set Covered by the Team40              | 6 |

| Project Management Style Adopted by the Team4 | 7 |

| Project Management Roles4                     | 7 |

| Team contract                                 | 8 |

# Table of Contents

## List of Symbols and Definitions

Efabless – Currently shutdown open-source fabrication company. Has provided many open-source tooling as well as the Caravel Harness

Caravel Harness - Provided wrapper around our design which includes an SoC

SoC - System on chip

ASIC - Application-Specific Integrated Circuit

RISC-V – Open-source ISA

PicoRV32 - A Size-Optimized RISC-V CPU

Chip Forge – ISU Club focused on developing and bringing up ASICs, who have also created a tool for testing caravel projects on an Xilinx Artix FPGA

CGRA – Coarse-Grained Reconfigurable Architecture, a reconfigurable architecture that operates on coarser granularity than traditional reconfigurable architectures such as FPGA

FPGA - Field Programmable Gate Array, reconfigurable integrated circuit

SPI - Serial Peripheral Interface

PCB - Printed Circuit Board

Verilog HDL - Verilog Hardware Description Language

SkyWater 130nm - Fabrication process used by Efabless

User Area - Our design space within the Caravel Harness

Management Area - Part of the Caravel Harness that includes management utilities, SoC, and logic analyzer probes

OpenLane - The collection of open-sourced tools provided by Efabless

Embench-iot – The collection of open-sourced benchmarks based on Bristol/Embecosm Embedded Benchmark Suite for modern embedded systems.

# Introduction

## Problem Statement

Processors are constrained by their defined instruction sets. If an operation isn't supported, designers face three options: redesign and refabricate the processor (which is costly and time consuming), approximate the operation using multiple instructions (which can be inefficient or inaccurate), or avoid the operation altogether. In many cases, none of these options are practical.

Currently, few research processors are suitable for learning processor design because most lack low-level accessibility and are difficult to modify. This forces students and educators to rely on alternative methods, which can limit hands-on learning.

To address this, we aim to design a system-on-chip (SoC) that allows users to define and implement custom instructions directly in the processor. Our goal is to make these instructions highly customizable, giving users maximum flexibility to tailor processor behavior to their needs. Additionally, because our team is interested in reconfigurable computing, this project will enable us to explore that field further by designing a dedicated reconfigurable computing unit.

For our ASIC design, we will use Efabless's Caravel platform along with the OpenLANE tooling. Efabless's Caravel will act as a harness that we will integrate our project into. This provides us with a management area that is powered by a VexRISC-V processor, including features such as logic analyzers, interrupt pins, and a wishbone bus including clock and reset signals, which we will use to support our design. OpenLANE is a collection of open-source tooling that we will use to generate the physical layout of our chip from the Verilog

code. Additionally, it also runs additional checks such as DRC (Design Rule Check), LVS (Layout Versus Schematic), and STA (Static Timing Analysis).

## Intended Users

### Chip Forge Club Member

Chip Forge is a student organization at Iowa State University dedicated to designing analog and digital ASICs. Each member has an interest in designing, testing, and/or fabricating ASICs. The club uses Efabless's Caravel and open-source tooling, so students need resources to help learn about it. Our project will provide students with an interactable ASIC to learn about the Caravel chip and serve as a potential jumping-off point for their projects.

### Hardware Students

Hardware students encompass all students learning about digital hardware design in classes like CPRE 2810, CPRE 3810, or CPRE/EE 4650. These students need ways to learn about reconfigurable ISAs and complete SoCs. The ways students learn about these topics is through software and FPGAs. Our project will provide a way for students to learn these things on a physical processor, which will aid in the education of many hardware students. Our project will also aid future students who use the Efabless process and Caravel chip in future senior design projects.

### Professors

Professors are interested in instructing their students and need new teaching methods. Our project provides an interactive way to teach students about open-source ISAs, and microprocessors. Our project will expand professors' teaching options and allow them to instruct their students more effectively.

# Requirements, Constraints, And Standards

## Requirements & Constraints

Functional requirements:

- Function as a microcontroller when provided with normal ISA instructions.

- Support custom instructions defined by the user.

- Custom instructions should only be executed when called (should not execute custom instructions when provided standard ISA instructions).

- Stores and runs programs provided by the user.

Technical requirements:

- HDL used is Verilog

- Custom instruction execution should not slow down the processer.

- Programming a new instruction should take minimal time.

- Max clock frequency of 40 MHz (constraint).

- The microcontroller is programmed using C.

- Design should pass LVS and DRC test before sending off to be fabricated.

- The ISA softcore used must be open-source.

- Chip tapeout in the SkyWater 130 nm process

User experiential requirements:

- Product should be user-friendly to program custom instructions and load in programs.

- Product should provide a wide range of settings that cater to different user experience levels.

- It should be easy to test custom instructions and programs.

- Custom instruction assembly code should be structured and loaded like a standard ISA instruction.

Physical:

- Must function at room temperature (≈20°C).

- User project must be 3mm x 3.6mm (10mm<sup>2</sup>) to fit in the user project area (constraint).

- Must use I/O pins provided by project wrapper (constraint).

### Engineering Standards

Engineering standards are important to adhere to when designing products. Standards ensure that your product is consistent with the industry, allowing easier use for users and others in the industry that may work on your product later. For our project, we will be using standards laid out by IEEE.

#### EEE 1754-1994: IEEE Standard for a 32-bit Microprocessor Architecture

Since we are designing a 32-bit Microprocessor, it is important for our project to adhere to the pre-established standards from IEEE. We be careful to ensure that we adhere to this standard when adding our custom function unit.

#### IEEE 1364-2001: IEEE Standard Verilog Hardware Description Language

The Efabless process requires the use of Verilog for our design. Using this, we will ensure our Verilog code adheres to the industry standard.

#### IEEE 1364.1-2002: IEEE Standard for Verilog Register Transfer Level Synthesis

Our project will use RTL synthesis to translate our Verilog code to a hardened design. Using this, we can write code that best works with RTL synthesis to ensure correctness and efficiency.

#### <u>Wishbone Bus</u>

Our project will use the wishbone protocol as implemented by Efabless to communicate between the user area and the management area. Efabless's process has this protocol implemented as a non-option, with a slight variation from the OpenCores wishbone protocol.

#### <u>SPI Protocol</u>

The SPI Protocol de facto standard is a serial communication bus that was developed by Motorola in the 1980s with a master-slave configuration that is commonly used in SD cards, it consists of four logic signals: CS, SCLK, MOSI, MISO. For our project the SPI Protocol will be used to communicate between off-chip memory and on-chip memory (the slaves) via a memory interface linked to an SPI master.

# **Project Plan**

# Project Management/Tracking Procedures

Our team will be using an agile management style for project planning. This allows our team to have structured goals with clear deadlines and milestones to reach, while also ensuring our team is provided with the flexibility needed to accommodate any unexpected difficulties that may arise during development.

Our team will track the progress through communication on Microsoft Teams and Discord as well as shared files in the SharePoint associated with the Teams. Additionally, we will be using GitLab for version control of code base and tracking any specific issues found in the code.

## Task Decomposition

Our project is split up into the following tasks which will be completed in sequential order:

- 1. Project Prep

- a. Setup virtual machines to complete design work on

- b. Setup Gitlab repos to hold source code and GitLab modules

- c. Become familiar with the Efabless tools

- i. OpenLane

- ii. Caravel

- d. Successfully harden and verify a test design

- 2. November Chip Design

- a. Decide on a design/component to place onto to chip framework

- b. Harden chosen design

- c. Pass precheck and verify functionality

- d. Work with dec24-12 to integrate our design into their chip

- 3. Project Design

- a. High level chip design

- i. Basic overview

- ii. Determine how softcore will interface with memory

- 1. Design cache system to interface with off chip memory

- iii. CyGRA integration

- iv. Interface with management area

- b. RISC-V core

- i. Determine available open-source IP designs

- ii. Choose the best open-source IP for our project

- iii. Test hardening the softcore to ensure compatibility

- c. Accelerator design (CyGRA)

- i. Determine acceleration use case

- ii. Design and verify hard coded accelerator

- iii. Backport work on hard coded accelerator to CyGRA

- d. RISC-V ISA extension

- i. Add basic instruction for testing

- ii. Integrate CyGRA into a custom instruction

- e. PicoRV32 test plan

- i. Create toolflow for testing

- 1. Behavioral

- 2. C code

- ii. FPGA testing flow

- 1. Compile embench-iot benchmarks

- 2. Run as baseline to compare to CyGRA acceleration

- f. Management area interface

- i. Determine how interrupts are supplied to processor

- ii. Determine how the management area will interface with on chip memory

- 4. Integration

- a. Combine memory system with softcore

- b. Connect CyGRA to the softcore

- c. Test memory system

- d. Integrate wishbone with management core

- 5. Testing/Verification

- a. Ensure full functionality of microcontroller

- b. Ensure implemented instruction works as expected

- c. Ensure memory interface is working correctly

- d. Run FGPA tests of full system and embench-iot benchmarks

- 6. Documentation

- a. Design documentation

- b. Design presentation

- c. Website design

- d. Bring up planning

#### Project Proposed Milestones, Metrics, and Evaluation Criteria

Our project's milestones are closely related to the main task sections listed above. Each of the milestones will be measured using the following metrics:

- Milestone 1: Complete tooling setup

- Each member of the team is able to fully harden a design and complete GL simulation on an example project.

- Each member can create a Verilog module and complete the steps above

- Each member is aware of how to use the virtual machines to harden a design

- Milestone 2: Small chip design

- Using a previously designed data path from a CPRE class, harden and verify the design

- Work with dec24-12 team to integrate our simple design into their framework

- Milestone 3: High level design and softcore

- Determine which open-source ISA softcore best fits our use case

- Ensure the chosen softcore works in the Efabless tooling

- Design high level of chip with included softcore

- Milestone 4: Accelerator/CyGRA design

- Determine the specific application to accelerate

- Develop simple Verilog module to accelerate use case

- Backport work to a CyGRA design

- Milestone 5: System Integration

- o Combine the CyGRA and the softcore

- Include on chip memory

- Wishbone bus integration to management core

- Milestone 6: Overall Design Testing

- Ensure the softcore can interface with both on and off chip memory through cache system

- Ensure the management core can write to the memory and reset the softcore

- $\circ~$  Ensure the custom instruction for the CyGRA works as intended

- Milestone 7: Synthesize Layout

- Synthesize each component individually

- o Synthesize high level design

- Perform gate level tests

- Milestone 8: Complete Documentation

- Complete all project documentation ensuring readability

- Finish any bring up documentation for the chip

### Project Timeline/Schedule

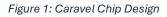

Our project is broken up into 6 major parts: Project prep and setup, November chip deadline, Project design, Integration, Testing, and Documentation. One of the first

deadlines is the November chip deadline (Figure 2). This included a full test of our team's knowledge of the Efabless tooling as well as our ability to work with another design team to integrate our design into their multi-design framework.

|       | Project Le                                      | ad     | Camden       |                |      |      |      | 16 Sep 2024 | 23 Sep 2024 | 30 Sep 2024 | 7 Oct 2024 | 14 Oct 2024 | 21 Oct 2024 | 28 Oct 2024                        | 4 Nov 2 |

|-------|-------------------------------------------------|--------|--------------|----------------|------|------|------|-------------|-------------|-------------|------------|-------------|-------------|------------------------------------|---------|

| WBS   | TASK                                            | LEAD   | START        | END            | DAYS |      | WORK |             |             |             |            |             |             | 28 29 30 31 1 2 3<br>M T W T F S S |         |

| 1     | Project Prep                                    |        |              | -              |      |      | -    |             |             |             |            |             |             |                                    |         |

| 1.1   | Chip forge Tutorials                            | ALL    | Mon 9/16/24  | Mon 9/30/24    | 15   | 100% | 11   |             |             |             |            |             |             |                                    |         |

| 1.2   | CprE 381 Lab hardening                          | Nick   | Mon 9/30/24  | Sun 10/27/24   | 28   | 100% | 20   |             |             |             |            |             |             |                                    |         |

| 1.2.1 | Lab 1                                           | Nick   | Tue 10/01/24 | Mon 10/07/24   | 7    | 100% | 5    |             |             |             |            |             |             |                                    |         |

| 1.2.2 | Lab 2                                           | Nick   | Tue 10/08/24 | Sun 10/27/24   | 20   | 100% | 14   | -           |             |             |            |             |             |                                    |         |

| 1.3   | RISC-v Knowledge                                |        | Mon 9/30/24  | Sun 10/06/24   | 7    | 100% | 5    |             |             |             |            |             |             |                                    |         |

| 1.4   | Acquire VMs for design                          | Camden | Mon 10/14/2  | 4 Mon 10/28/24 | 15   | 100% | 11   |             |             |             |            |             |             |                                    |         |

| 1.4.1 | Access VM                                       |        | Tue 10/15/24 | Wed 10/16/24   | 2    | 100% | 2    |             |             |             |            |             |             |                                    |         |

| 1.4.2 | Get basic setup done                            |        | Thu 10/17/24 | Fri 10/18/24   | 2    | 100% | 2    |             |             |             |            |             |             |                                    |         |

| 1.4.3 | Get required software installed                 |        | Sat 10/19/24 | Thu 10/24/24   | 6    | 100% | 4    |             |             |             |            |             |             |                                    |         |

| 1.4.4 | Test software to ensure functionality           | ALL    | Fri 10/25/24 | Mon 10/28/24   | 4    | 100% | 2    |             |             |             |            |             |             |                                    |         |

| 2     | Nov Chip 11/11/24                               |        |              | -              |      |      | -    |             |             |             |            |             |             |                                    |         |

| 2.1   | Passing precheck                                | Nick   | Fri 10/25/24 | Tue 10/29/24   | 5    | 100% | 3    |             |             |             |            |             |             |                                    |         |

| 2.2   | Confirm working                                 | Nick   | Tue 10/29/24 | Sat 11/02/24   | 5    | 100% | 4    |             |             |             |            |             |             |                                    |         |

| 2.3   | Work with dec24-12 to get design<br>implemented | Nick   | Wed 10/30/2  | 4 Thu 11/07/24 | 9    | 100% | 7    |             |             |             |            |             |             |                                    |         |

Figure 2: Project Prep and November Chip

Our next deadline is focused on the full design and chip tapeout/submission.

Figure 3: Project Design

Our Gantt chart has been mostly focused on the immediate future with less detailed objectives filling out the rest to give a rough outline of what still needs to be completed as seen in figure 2 and figure 3.

| 6     | Documentation                   |        |              | -            |    |     | -  |  |

|-------|---------------------------------|--------|--------------|--------------|----|-----|----|--|

| 6.1   | Design doc (add sub tasks here) | ALL    | Fri 11/01/24 | Thu 12/05/24 | 35 | 70% | 25 |  |

| 6.1.1 | Executive Summary               | ALL    | Mon 11/11/24 | Thu 11/21/24 | 11 | 60% | 9  |  |

| 6.1.2 | Introduction                    | ALL    | Wed 11/13/24 | Sat 11/23/24 | 11 | 90% | 8  |  |

| 6.1.3 | Requirments                     | ALL    | Fri 11/15/24 | Mon 11/25/24 | 11 | 60% | 7  |  |

| 6.1.4 | Project Plan                    | Camden | Sun 11/17/24 | Wed 11/27/24 | 11 | 40% | 8  |  |

| 6.1.5 | Design                          | Calvin | Tue 11/19/24 | Fri 11/29/24 | 11 | 10% | 9  |  |

| 6.1.6 | Implementation                  | Levi   | Thu 11/21/24 | Sun 12/01/24 | 11 | 0%  | 7  |  |

| 6.1.7 | Professional Responsibility     | John   | Sat 11/23/24 | Tue 12/03/24 | 11 | 0%  | 7  |  |

| 6.1.8 | Closing                         | ALL    | Mon 11/25/24 | Thu 12/05/24 | 11 | 0%  | 9  |  |

| 6.2   | Design Presentation             | ALL    | Fri 11/01/24 | Thu 12/05/24 | 35 | 5%  | 25 |  |

| 6.3   | Website design                  | Levi   | Fri 11/01/24 | Thu 12/05/24 | 35 | 70% | 25 |  |

#### Figure 4: Documentation

Figure 4 represents some of our documentation objectives that (at the time) were to be completed. You can see that they are staggered as each section built upon the last.

| 4       | Integration                         |        |              | -            |    |     | -    |  |

|---------|-------------------------------------|--------|--------------|--------------|----|-----|------|--|

| L1      | [Task]                              |        |              |              | 1  | 0%  |      |  |

| 1.2     | [Task]                              |        |              |              | 1  | 0%  |      |  |

| 1.3     | [Task]                              |        |              |              | 1  | 0%  |      |  |

| 5       | Testing/Verification                |        |              |              |    |     | -    |  |

| 5.1     | Test PicoRV32                       |        |              |              | 1  | 0%  |      |  |

| 5.1.1   | Test Base Pico                      |        |              |              |    |     |      |  |

| 5.1.1.1 | Behorial Testing                    |        |              |              |    |     |      |  |

| 5.1.1.2 | Test Using C code                   |        |              |              |    |     |      |  |

| 5.1.2   | Test Custom Instruction             |        |              |              |    |     | -    |  |

| 5.1.2.1 | Behorial Testing                    |        |              |              |    |     |      |  |

|         | Test Using C code                   |        |              |              |    |     |      |  |

| 5.2     | Test CyGRA                          |        |              |              | 1  | 0%  |      |  |

| 5.2.1   | Behorial Testing                    |        |              | -            |    |     |      |  |

| 5.2.2   | Test Using C Code                   |        |              | -            |    |     |      |  |

| 5.3     | Test Integration                    |        |              |              |    |     | 14   |  |

| 5.3.1   | Test With Direct Connection to Memo | ory    |              |              |    |     | 14.1 |  |

| 5.3.2   | Test With Simple Accelerator        |        |              | -            |    |     | 4    |  |

| 5.3.3   | Test With Simple CyGRA              |        |              | -            |    |     | -    |  |

| 6       | Documentation                       |        |              |              |    |     | -    |  |

| 5.1     | Design doc (add sub tasks here)     | ALL    | Fri 11/01/24 | Thu 12/05/24 | 35 | 70% | 25   |  |

| 5.1.1   | Executive Summary                   | ALL    | Mon 11/11/24 | Thu 11/21/24 | 11 | 60% | 9    |  |

| 5.1.2   | Introduction                        | ALL    | Wed 11/13/24 | Sat 11/23/24 | 11 | 90% | 8    |  |

| 5.1.3   | Requirments                         | ALL    | Fri 11/15/24 | Mon 11/25/24 | 11 | 90% | 7    |  |

| 5.1.4   | Project Plan                        | Camden | Sun 11/17/24 | Wed 11/27/24 | 11 | 90% | 8    |  |

| 5.1.5   | Design                              | Calvin | Tue 11/19/24 | Fri 11/29/24 | 11 | 90% | 9    |  |

| 5.1.6   | Implementation                      | Levi   | Thu 11/21/24 | Sun 12/01/24 | 11 | 90% | 7    |  |

| 5.1.7   | Professional Responsibility         | John   | Sat 11/23/24 | Tue 12/03/24 | 11 | 90% | 7    |  |

| 5.1.8   | Closing                             | ALL    | Mon 11/25/24 | Thu 12/05/24 | 11 | 90% | 9    |  |

| 5.2     | Design Presentation                 | ALL    | Fri 11/01/24 | Thu 12/05/24 | 35 | 5%  | 25   |  |

| 5.3     | Website design                      | Levi   | Fri 11/01/24 | Thu 12/05/24 | 35 | 70% | 25   |  |

Figure 5: Integration, Testing/Verification, and Documentation

### Risks and Risk Management/Mitigation

Due to our open-ended project, there are a few risks that are quite different from other groups.

One major risk that we face is that our project may become unfeasible due to time constraints. However, this risk is fairly minimal due to the guidance that our advisor, Dr. Duwe, gives us during our weekly meetings. This ensures that we will end up with a complete project by the end of the year. While unlikely, if the feasibility of our project is at

risk later in the project, we plan to mitigate this by developing a fallback plan to ensure that we can deliver a functional product in the event of major setbacks.

Another significant risk we face is the potential for time delays, as before this project we were not familiar with Efabless's Caravel or OpenLANE tools. This lack of experience increases the likelihood of unexpected challenges that could slow our progress. While minor setbacks alone may not have any serious consequences on our timeline, persistent delays could lead to larger problems later on. To mitigate this risk, we are adopting an agile management approach, allowing us to address issues more effectively as they arise. Additionally, we are prioritizing clear and consistent communication within our team to ensure we keep steady progress and quickly resolve roadblocks.

The largest challenge we've faced so far is the time required to complete certain components, the most notable of which is the CyGRA, which has proven to be much more complex than anticipated. Additionally, the SPI master unit took us longer than expected to adapt to our project which caused delays in integration and testing. To mitigate this, we have split our team into multiple leads so during any delay, other members can continue with other modules of the chip to keep us on track.

## Personnel Effort Requirements

Our task list is constantly evolving, making it difficult to assign expected work hours to dedicated tasks. Time estimates can be easily skewed by factors such as the number of work sessions and length of time spent by each member, which can vary in efficiency depending on the day.

| Task                 | Projected Hours | Actual                 |

|----------------------|-----------------|------------------------|

| Workflow Tools/Setup | 40 Hours        | 40 Hours               |

| November Chip Design | 20 Hours        | 30 Hours               |

| Project Design       | 100 Hours       | 200 Hours              |

| Integration          | 60 Hours        | 100 Hours              |

| Testing/Verification | 40 Hours        | Ongoing (currently>50) |

| Documentation        | 40 Hours        | Ongoing (currently>40) |

Table 1: Projected Hours

We have completed design and individual testing of all our modules, and are currently working on integration of major components such as the CyGRA into our microcontroller. We underanticipated how complex our CyGRA would be, which has been a major contributing factor to our design time.

# Other Resource Requirements

Tools and work environments that are beneficial to larger team productivity have been very helpful in this project. As such, we contacted ISU's ETG (Electronic and Technology Group) that helps support senior design teams to create a virtual machine to work on. This has allowed us to work collaboratively remotely and ensure our environment has identical variables to reduce errors relating to the setup of the tools we use. We have used this virtual machine to build the RISC-V toolchain as well as generate benchmarks from embench-iot.

Beyond this, we have also accessed and used the tools provided by the ISU ChipForge club. This has allowed us to run system tests on an Artix FPGA board in Durham, which has provided valuable feedback on our design and development.

# Design

## Design Context

### Broader Context

One of our main goals in designing this project was to keep the technology accessible. To support this, we used only open-source tools and made all our designs open-source, allowing others to expand and improve upon them. This ensures that our final deliverable serves as a valuable education and research resource to help other students and teams gain entry into the field of hardware design.

Below is a table of some considerations we made when designing and developing our project:

| Area                         | Description                | Example                      |

|------------------------------|----------------------------|------------------------------|

|                              |                            | Our product gives students   |

|                              |                            | hands-on experience with a   |

|                              | How does your project      | real processor fabricated    |

| Public Health, safety, and   | affect the general         | on an IC rather than         |

| welfare                      | well-being of various      | software simulations and     |

| wettale                      | stakeholder groups?        | FPGAs. The programmable      |

|                              | stakenotuer groups:        | aspect of the project can    |

|                              |                            | help students test designs   |

|                              |                            | and learn Hardware design.   |

|                              | How well does your project | Our project adds to the list |

| Global, cultural, and social | reflect the values,        | of open-source designs that  |

|                              |                            | the global electrical and    |

|             | practices, and aims of the  | computer engineering       |  |  |

|-------------|-----------------------------|----------------------------|--|--|

|             | cultural groups it affects? | community can use and      |  |  |

|             |                             | expand upon.               |  |  |

|             |                             | Custom instruction can     |  |  |

|             | What environmental impact   | make some processes take   |  |  |

| Environment | might your project have?    | less instructions and less |  |  |

|             | might your project have?    | energy, which can add up   |  |  |

|             |                             | when done many times.      |  |  |

|             |                             | Our product is open source |  |  |

|             |                             | which lets anyone use it.  |  |  |

| Economic    | What economic impact        | This saves people from     |  |  |

| Economic    | might your project have?    | having to develop a design |  |  |

|             |                             | of their own, which saves  |  |  |

|             |                             | them money.                |  |  |

|             | TILOD I O I I               |                            |  |  |

Table 2: Broader Context

### Prior Work/Solutions

#### Nios® V/g General purpose Processor from Intel

• Processor Overview:

https://www.intel.com/content/www/us/en/docs/programmable/683632/24-3/processor-87132.html

- o 32-bit RISC-V processor

- FPGA implementation of processor

- Come with Quartus® Prime Pro Edition

- Custom Instruction Overview:

https://www.intel.com/content/www/us/en/docs/programmable/773194/current/p rocessor-custom-instruction-overview.html

- Processors support non-branching custom instructions

- Selected by a mux choosing between the ALU and Custom Instruction Unit during the execution state of the pipeline.

- Benefits and Drawback compared to our design

- $\circ$  Benefits:

- Supports 32 Custom Logic Blocks

- Has an Integer Multiplication and Division Unit

- Has a floating-point unit

- Pipelined

- Faster frequency max on popular FPGAs

- o Drawbacks:

- FPGA based

- Required user to have an FPGA

- Larger Area

- Can not fabricate as an IC

- Cannot re-program custom instruction during run time

- Not free (requires Quartus<sup>®</sup> Prime Pro Edition)

#### Arm Custom Instructions

- Paper: <u>https://armkeil.blob.core.windows.net/developer/Files/pdf/white-paper/arm-custom-instructions-without-fragmentation-whitepaper.pdf</u>

- Available with Cortex M33, Cortex-M55, and Cortex-M85

- Arm Architecture

- Programable Instruction

- Used in the Execution stage of the pipeline

- Benefits and drawbacks compared to our solution

- o Benefits

- Available on Arm processors

- More features

- Faster

- Custom Instruction solution more intricate

- Can pipeline custom instruction

- o Drawbacks

- Neither Arm nor Arm Custom Instructions is open source

- Complicated to use

Sources with citations:

[1] "4. Nios<sup>®</sup> V/g Processor," Intel, 2024.

https://www.intel.com/content/www/us/en/docs/programmable/683632/24-3/processor-87132.html (accessed Dec. 08, 2024).

[2] "1. Nios<sup>®</sup> V Processor Custom Instruction Overview," Intel, 2023.

https://www.intel.com/content/www/us/en/docs/programmable/773194/current/process or-custom-instruction-overview.html (accessed Dec. 08, 2024).

[3] J. Yiu, "Innovate by Customized Instructions, but Without Fragmenting the Ecosystem," 2021. Accessed: Dec. 08, 2024. [Online]. Available:

https://armkeil.blob.core.windows.net/developer/Files/pdf/white-paper/arm-custominstructions-without-fragmentation-whitepaper.pdf

### Technical Complexity

Our project has multiple complex components that need to work together. Finishing the project will require the following tasks.

- Deciding on an open-source ISA softcore to serve as the main compute unit

- Creating a CyGRA (Coarse-Grained Reconfigurable Architecture) co-processor to implement custom instructions

- Designing a memory interface and caching unit to manage on- and off- chip memory

- Implementing a SPI master interface to communicate with the off-chip SRAM

- Modify a Wishbone slave interface to enable communicate and data transfer to the user project area (including writing processor code to memory)

- Integrate all components into a complete system, allowing users to configure the CyGRA to execute custom instructions alongside the main softcore

## **Design Exploration**

### Design Decisions

For our project, we made several important design decisions, outlined below:

- Using an open-source ISA

- o Selected the RISC-V ISA

- o Simple, fully open-source, widely adopted

- o Commonly used and taught in universities and research settings

- Selecting the PicoRV32 softcore

- o Relativity easy to integrate into our design

- o Includes a built-in co-processor interface, simplifying integration of the CyGRA

- o Size-optimized, occupying only 0.6 x 0.6 mm<sup>2</sup> within the SkyWater 130nm process

- Implementing a Coarse-Grained Reconfigurable Architecture (CyGRA) for custom instructions

- o Complex module to design

- o Challenging to integrate effectively into the overall system

- o New area for our team, requiring new research and learning

An important consideration throughout our design process was ensuring that all chosen components and designs were fully compatible with the Efabless Caravel platform and toolchain. Every decision had to account for both smooth integration between components and support within the Caravel wrapper. This was the main reason we did not consider the MIPS ISA, despite our team having experience with it through various ISU classes.

#### Ideation

When looking for an open-source processor design, we had some suggestions from our advisor and found options online. Below are the designs we found and considered.

| Rocket Chip                            | Neorv32                                                                                            | Vex RISC-V                                                                 | CVA6    | PicoRV32                                                                                                           |

|----------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------|

| - Feature rich<br>- Not size optimized | - RISC-V 32 bit<br>- Designed as a<br>microcontroller<br>- Not size optimized<br>- Written in VHDL | - Highly customizable<br>- Not size optimized<br>- Written in<br>SpinalHDL | svstems | - RISC-V 32 bit<br>- Wishbone interface<br>and high clock<br>frequency<br>- Size optimized<br>- Written in Verilog |

Table 3: Comparison of various softcores that were considered for our project

### Decision-Making and Trade-Off

When deciding between the different RISC-V softcore designs we established a few criteria to rank the designs we found. The criteria are as follows:

- Instruction Set

- o Used to categorize processors based on their supported architecture (32-bit or 64-bit)

- o Determine which processors supported the most extensions of their given ISA (i.e. RV32I vs RV32IM)

- Written Language

- o Since the Efabless process and Caravel requires designs in Verilog, we prioritized processors written in Verilog for ease of integration

- Features

- o Assessed additional capabilities included in the base design, such as Linux compatibility or built-in Wishbone interface

- Size Optimization

- Considered whether the processor's repository specifically mentioned size or space optimization – critical to our design as the Efabless Caravel has a limited user area of 2.92 mm x 3.52 mm (10mm<sup>2</sup>), which must fit both the processor, memory, and custom co-processor

After consideration, we decided to use the PicoRV32 as our RISC-V softcore. The reason that we decided on this was for a couple of reasons. First off, it was written in Verilog which

allows us to easily integrate it into the Efabless Caravel. Secondly, it is a size optimized design, which is important considering the space available in the user area, allowing us to dedicate more space to other components. Lastly, it includes a Wishbone interface, which we can use to integrate with the management area of the Caravel.

# **Final Design**

### Overview

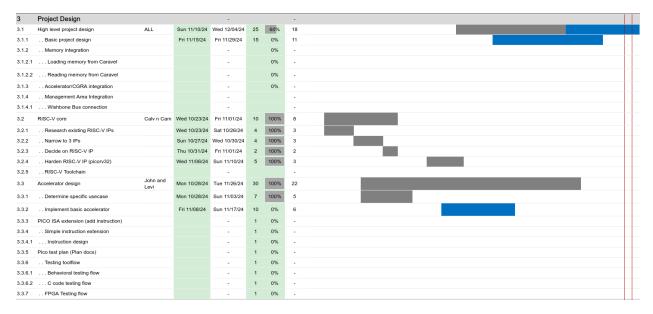

Figure 6: High-level design contained within the user area

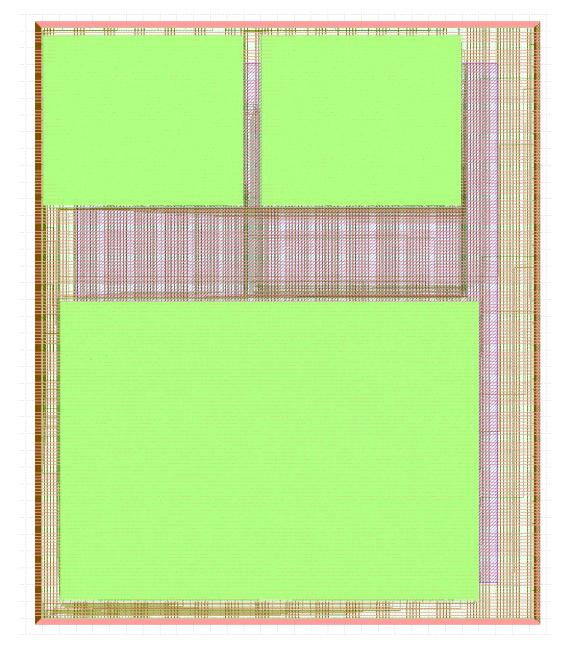

Figure 7: Synthesized Layout of Circuit

The high-level design (as seen in figure 6) consists of two main areas, the management area, and the user project area. The management area is provided as is from Efabless and contains a VexRISCV processor integrated with a Wishbone which provides the clock, reset, and buses for communication into the user project area. Additionally, the management area provides logic analyzers so that after fabrication you can still probe sections of the user area for testing to ensure things are working as expected. The management area also has flash inputs which allows the user to load programs onto the VexRISCV processor.

The user project area is a ~10mm<sup>2</sup> section where our design is placed into. It has access to 34 GPIO ports, allowing us to set them as either input or output depending on what is needed, such as for the off-chip memory as seen in figure 6. Within the user area is the PicoRV32, CyGRA, memory system, and cache memory.

Figure 7 shows the synthesized layout of the user\_project\_wrapper. The larger rectangle on the bottom is the wrapper containing the PicoRV32, Memory System, and CyGRA. The wrappers area is 2.5 mm x 1.8mm which is 4.5 mm^2. The two smaller rectangles on the top are the DFFRAM modules, they both have an area of about 1mm^2.

### Detailed Design and Visuals

#### PicoRV32

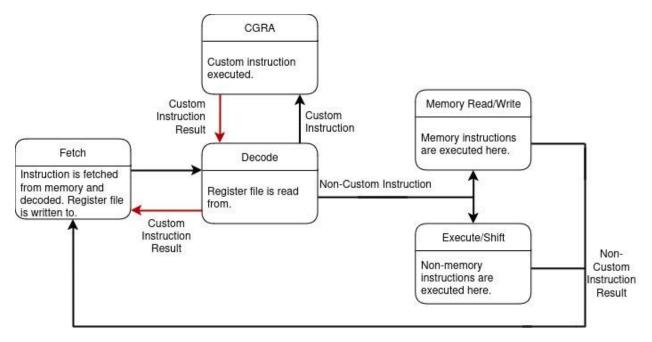

The PicoRV32 is a size optimized RISC-V 32-bit processor, which we have chosen to be the main compute unit for our design. The PicoRV32 is a non-pipelined processor, meaning that it only runs a single stage at a time (as shown in figure 8).

#### Figure 8: PicoRV32 Datapath

This processor supports the full set of standard 32-bit RISC-V instructions but also allows for custom instructions through a co-processor interface, which triggers when an unknown instruction is decoded. We leverage this interface to seamlessly integrate the CyGRA with minimal overhead into the main processor. Below is an example of how the pipeline operates with the CyGRA:

- 1. Fetch stage

- a. Fetch the next instruction from memory

- b. Decode the fetched instruction and set control signals

- c. Write back the results of the previous instruction to the register file (if needed)

- 2. Decode stage Splits into one of five stages (listed below)

- a. Memory read: for load instructions

- b. Memory write: for store instructions

- c. Shift: for shift operations

- d. Execute: for all other standard instructions

- e. CyGRA: for custom instructions handled by the CyGRA

Once a stage is completed, control returns to the Fetch stage. The memory Read and Write, Shift, and Execute stages all transition directly back to Fetch. However, the CyGRA stage routes through an additional Decode stage before returning to Fetch. Below is a table showing the cycles per instruction (CPI) for standard (non-custom) instructions, as documented in the PicoRV32 readme, along with their runtimes based on a 40 MHz clock speed (the max clock speed provided in Caravel).

| Instruction | Jump and<br>link | ALU reg +<br>Immediate | ALU reg + reg | Branch (not<br>taken) | Memory load | Memory<br>store | Branch<br>(taken) | Indirect<br>jump | Shift<br>operations |

|-------------|------------------|------------------------|---------------|-----------------------|-------------|-----------------|-------------------|------------------|---------------------|

| CPI         | 3                | 3                      | 3             | 3                     | 5           | 5               | 5                 | 6                | 4-15                |

| Runtime     | 75 ns            | 75 ns                  | 75 ns         | 75 ns                 | 125 ns      | 125 ns          | 125 ns            | 150 ns           | 100ns-<br>375 ns    |

Table 4: Expected CPI and runtime for the PicoRV32

Note: The memory figures above assume single cycle read/write memory, which is unrealistic for our project. A cache hit may produce a CPI and runtime like above, but a cache miss would result in a high CPI and slow runtime due to SPI being only able to transfer one bit at a time

Our aim for custom instructions is to take 3-30 CPI depending on which instruction is being executed, meaning that the runtime would range from 75ns to 750ns.

The PicoRV32 writes and reads memory over our implemented memory interface (described later in this section).

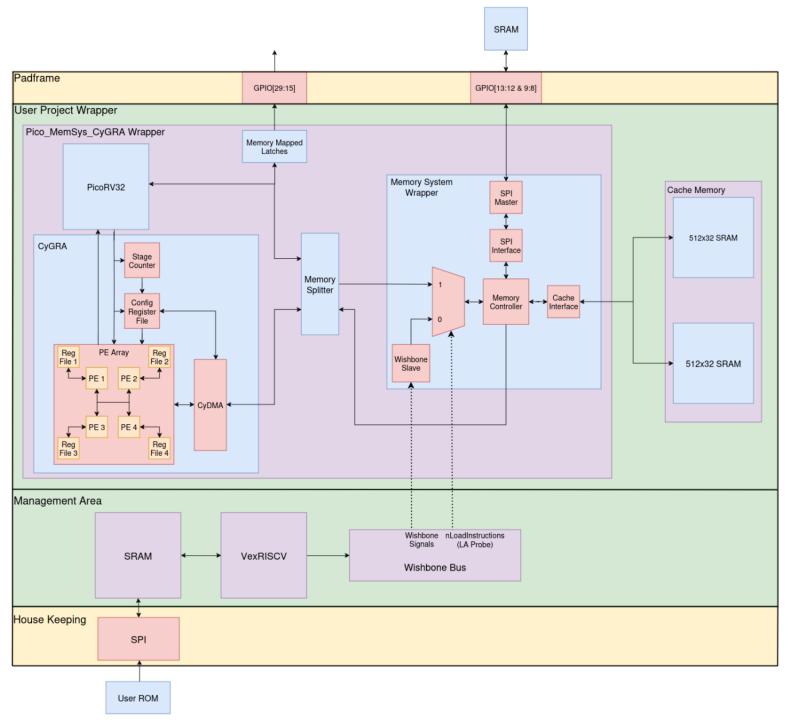

#### CyGRA

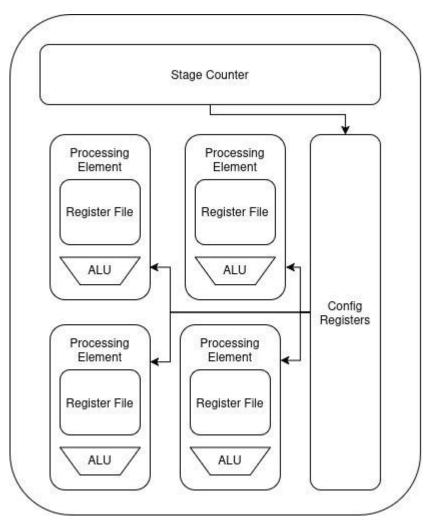

The CyGRA is our custom coprocessor consisting of an array of 4 processing elements arranged in a 2 by 2 grid that is capable of reading and writing directly to and from memory. Each processing element contains its own register file, containing 32 registers, and this helps lower the amount of DMA or DMO commands that are necessary. There is a stage counter which keeps track of the amount of stages/cycles that will be necessary for the command to work appropriately.

Figure 9: CyGRA

#### **Processing Elements**

Each processing element consists of an ALU, register file, and input muxes capable of integer arithmetic as well as data passthrough. Each processing element is capable of 4 operations: addition, subtraction, multiplication and passthrough. Passthrough is used to enable shuffling of data between register files.

#### Memory System

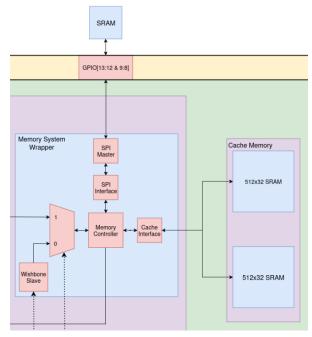

Figure 10: Memory subsystem

The Memory System provides interfaces for the Wishbone Slave, PicoRV32, and CyGRA to interact with. The Memory System decides which component has access to memory. If nLoadInstructions is low, then only the Wishbone Slave access memory. If nLoadInstructions is high, then either the PicoRV32 or CyGRA can access memory. The PicoRV32 has priority over the CyGRA (If both try to access memory, the PicoRV32 will be given access.)

The Memory System manages memory between the On-chip cache memory and Off-Chip SRAM. The Memory System uses a write-through cache with a write allocation policy, meaning the cache will get written on all writes and read misses. This results in considerable performance improvements when running programs.

#### On-chip memory

Consists of two pre-hardened open source 512x32 DFFRAM modules. This works as cache memory for higher performance. It works in tandem with the Off-chip memory to ensure a large but fast memory system.

#### Off-chip memory

512 Kbit SRAM PMOD module that communicates with the design over SPI. This acts as the RAM as seen in a typical system, allowing us to load larger programs without using the entire user space for memory

#### SPI master unit

The SPI master unit is a modified Efabless SPI master unit, designed to allow the memory controller to read and write, over SPI, to the off-chip SRAM PMOD module.

#### Wishbone slave

Reads data sent from the Management Area. The Management Area sends instruction memory and other data needed for programs to run on the PicoRV32. This includes programming the memory for the PicoRV32 to run programs.

### Functionality

The user can write a C program, which can be compiled to hex by the make\_firmware.py python script. This hex can be flashed to the Caravel chip using ChipForge tools (documentation on how to do this is provided in the ChipForge GitLab).

After flashing the hex firmware, instruction memory will be written to the user area memory using the Wishbone bus. During this process, the PicoRV32 remains idle, waiting for nLoadInstructions to go high. Once the VexRISCV completes writing, nLoadInstruction goes high and the PicoRV32 begins reading instructions from memory and executes them.

Our CyGRA is designed so that the user first loads a configuration, then inputs data, and can repeatedly execute the same configuration with different data without reloading the configuration. A configuration consists of the dataflow of where each processing element receives its data from, which address in its own register file that it writes to, and what operation it performs on the input data. Combined with the ability to specify multiple stage configurations, where for each clock cycle that the CyGRA executes, a new configuration is used, complex dataflows such as linear algebra operations or FFT are facilitated.

We have created a file that includes how to encode your own functions and common functionality and computations that we can use. For example, we have a function called mac(), this will allow anyone unfamiliar with the project to perform their own multiply and accumulate function without knowing anything about the CyGRA itself. We also have DMA, DMO, CFG, and COM commands which with the proper inputs will create custom instructions for the user to use, without little to no knowledge of the CyGRA. All these functions can be used in a user's own program to help accelerate whatever they desire.

### Areas of Challenge

One of the major challenges we faced during development was the CyGRA. Initially, it was difficult to determine how to structure it as we weren't sure which functions we wanted to accelerate. Even after identifying our target functions, we struggled to find the best design approach. We quickly learned that aiming for a perfect solution from the start was

unrealistic; progress came through iteration and experimentation. Over the course of development, we revised the CyGRA design four or five times to better meet our needs and improve various features such as useability and complexity. This iterative process was essential, and we learned that the most important step is often just getting started even if the initial design isn't perfect.

This iterative process also gave us valuable opportunities to receive feedback from our advisor, Dr. Duwe. With each new design iteration we presented, he provided us with insightful feedback and pointed us towards additional resources to refine and strengthen our approach. This cycle of improvement continued until we arrived at our final design that we are very proud of.

Overall, we successfully met our client's goals by delivering a non-trivial design that enables students to engage hands-on with bringing up a new chip for the ISU ChipForge club, while also exploring advanced technologies like Coarse-Grained Reconfigurable Architecture.

### **Technology Considerations**

The Efabless design process requires the use of specific open-source tools, with OpenLANE being the primary tool. While these tools are well-documented, they are not particularly user-friendly, which can make them challenging to use at times. Fortunately, Efabless provides scripts and configuration files that automate much of the process, allowing us to complete most tasks without needing to delve deeply into the inner workings of each individual tool.

# Testing

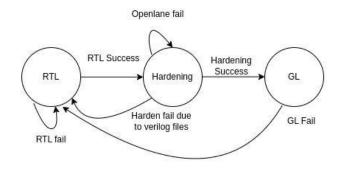

Our overall testing plan is illustrated in Figure 11. In summary, we begin by running testbenches for each individual module using Questasim. Once these pass, we proceed to RTL simulation of the fully integrated system, where we run system-level tests using Cocotb to verify correct functionality. Next, we perform FPGA testing to confirm the design operates correctly on physical hardware; this stage also allows us to test GPIO functionality, such as interfacing with the SRAM PMOD module. Finally, we conduct gate-level tests of the complete system to ensure the chip's hardening process did not introduce any errors.

Figure 11: A state diagram showing the testing flow we used during the project

## Unit Testing

- PicoRV32

- o Tested with QuestaSim testbenches

- o Verified reading and executing instructions and programs in RTL simulation

- Working merge and bubble-sort

- CyGRA

- Tested with QuestaSim

- Validate custom instruction execution

- Test each CyGRA component independently

- Test entire integrated unit

- Internal Memory

- Testing using Questa Sim

- Verify direct read/write operations

- Verify read/write operations through memory interface

- Tested instruction fetching and memory reading and writing in RTL simulation

### Interface Testing

- Wishbone Slave

- o QuestaSim

- Writing memory interface instructions

- o RTL simulation

- Writing a series of memory interface instructions (PicoRV32 instruction memory) from management area.

- Memory Interface

- o QuestaSim

- Reading/Writing memory into simulated external (non-SPI) and internal memory.

- The above tested using Wishbone Slave and PicoRV32.

- o RTL simulation

- Writing instruction memory through the wishbone bus.

- Reading and Writing memory from external memory using simulated Verilog module of SRAM.

- Cache operations for all scenarios (Write, Read Miss, and Read Hit)

- SPI Main

- QuestaSim

- Reading and writing from simulated SPI Slave.

- Reading and writing instructions through memory interface.

- o RTL simulation

- Reading memory based on signals from Memory Interface and simulated SRAM.

### Integration Testing

- Wishbone Slave, Memory Interface, SPI Main, External Memory.

- Path while writing instruction memory from management area.

- QuestaSim

- Fully tested writing memory via simulated Wishbone inputs.

- o RTL simulation

- Fully tested writing instruction memory via Wishbone.

- PicoRV32, Memory Interface, Internal Memory, External Memory, SPI Main.

- $\circ$  Path involved with the execution of non-custom instructions.

- QuestaSim (excluding SPI Main memory)

- Fully tested reading/writing memory and non-memory instructions

- RTL simulation

- Tested several example C programs that cover all RISCV321 instructions

- CyGRA, PicoRV32, Memory Interface, Internal Memory, External Memory, SPI Main.

- $\circ$  Path involved with the execution of custom instructions.

- o RTL simulation

- Tested MAC and FFT programs using custom instructions

# System Testing

- RTL Simulation

- $\circ$   $\,$  Tested Mac and FFT programs using custom instructions  $\,$

- FPGA Testing

- Running embench-iot benchmarks, we modified them for our system so that the benchmarks will run as standalone files, removed all dependencies to libraries and other things that is not on the FPGA, and created 2 variants for each benchmark, one that is standard and another that has our CyGRA being utilized and executing.

# **Regression Testing**

Our regression testing framework ensures that changes to the project do not unintentionally alter the expected behavior. We leverage CI/CD pipelines for each repository to automatically run regression testing whenever changes are committed. The pipeline executes relevant testbenches for all files, and if any test fails, the issue is flagged in the pipeline and team members are notified via email to prevent further regression. When a change in behavior is intentional, we document it clearly and update the corresponding testbenches to align with the new requirements.

## Acceptance Testing

Our acceptance testing ensured that we met the key performance metrics defined earlier, which are critical to verifying that the CyGRA delivers the expected impact. After hardening our design, we will validate that the user area passes Efabless's precheck process, confirming that the physical layout matches the Verilog design. The Efabless precheck also runs DRC and LVS tests to identify any potential fabrication issues, ensuring the design is ready for production.

### Results

The results from our tests primarily take the form of waveform outputs, which provide a detailed view of signal behavior. These waveforms were carefully analyzed to verify that the design meets our defined performance and functional metrics, such as correct instruction execution, timing accuracy, and data integrity. Beyond initial validation, waveform comparisons also played a key role in our regression testing framework. By using waveform-based verification, we could see that any changes to the design do not unintentionally later the expected behavior. Automated tools (like CI/CD) are employed,

when possible, to check results of testbenches, allowing us to quickly identify issues and address them before they escalate.

Since the CyGRA took much more time than anticipated to design. We didn't have much time to test its functionality. Currently, we know it works properly for single configuration instructions but are unsure of instructions with more than one configuration. We also haven't had time to do FPGA or GL tests, which are important to verify if our fabricated chip would function properly.

# Implementation

We have currently built a product that is able to execute custom instructions as described in our final design sections. We have also synthesized a layout via OpenLANE that could theoretically be fabricated, although the project is not in a state where it should be synthesized due to the lack of FPGA and GL tests. Hopefully, these tests can be performed in the future to verify the functionality of our project so it can be synthesized.

## **Design Analysis**

The design is currently able to run all C programs that don't contain any custom instructions. This has been verified with many C programs. Our CyGRA can execute all single config instructions and some multi-config instructions. We have arrived at this conclusion based on the current testing we have done (MAC and FFT).

# **Ethics and Professional Responsibility**

Our team defines engineering ethics as a commitment to uphold the integrity, transparency, and accountability in all aspects of our project. For our project, professional responsibility extends to producing open-source hardware and software that contributes positively to the academic and engineering community. Throughout the project, we have aimed to act in good faith, communicate openly, and ensure that all decisions we have made are backed by solid engineering principles. Our overarching philosophy is that engineering education should be accessible, ethical, and contribute to the betterment of the broader community.

| Area of<br>Responsibility   | Definition                                                                                                                                                                                                                                       | Corresponding IEEE<br>Ethics Code                                                                                                                                                                                         | Team interaction                                                                                                                                                                                                                                                    |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Work<br>Competence          | Our definition of work<br>competence is making<br>sure that we are<br>working to the best of<br>our abilities and that we<br>are being honest with<br>each other if we are not<br>completely confident in<br>our abilities to perform<br>a task. | 6. to maintain and<br>improve our technical<br>competence and to<br>undertake technological<br>tasks for others only if<br>qualified by training or<br>experience or after full<br>disclosure of pertinent<br>limitations | Our team ensured that<br>we carried out each<br>task to the best of our<br>ability given time<br>constraints and tried<br>not to promise<br>anything we couldn't<br>deliver and addressed<br>limitations                                                            |

| Financial<br>Responsibility | Our definition of<br>financial responsibility<br>is making sure that we<br>are not misusing funds<br>for our project and<br>making sure that we are<br>making it properly open<br>source so that others<br>can learn from our work               | <b>4.</b> To reject bribery in all its forms                                                                                                                                                                              | Our team ensured that<br>our project was<br>completely open<br>source and at the<br>minimum cost to<br>anyone wanting to<br>replicate our work and<br>were transparent with<br>our client and<br>stakeholders on the<br>cost of production or<br>desired components |

# Areas of Professional Responsibility/Codes of Ethics

| Communication<br>Honesty      | Our definition of<br>communication<br>honesty is making sure<br>that we are being<br>honest with how and<br>what our project can<br>perform as well as<br>being honest with our<br>team members and our<br>client/advisor | <b>3.</b> To be honest and realistic in stating claims or estimates based on available data                                                                                                                                                                                                           | We maintained clear<br>and honest<br>communication with<br>all stakeholders<br>ensuring our technical<br>reports and progress<br>were reported<br>accurately                                                                 |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Health, Safety,<br>Well-being | Our definition of health,<br>safety, and well-being is<br>making sure that we are<br>making a project that<br>will improve people's<br>lives through learning<br>and not negatively<br>affect others                      | 1. to hold paramount the<br>safety, health, and<br>welfare of the public, to<br>strive to comply with<br>ethical design and<br>sustainable development<br>practices, to protect the<br>privacy of others, and to<br>disclose promptly factors<br>that might endanger the<br>public or the environment | Our team focused on<br>the technical<br>development of our<br>project and disclosed<br>any information that<br>could be problematic<br>in a digital<br>environment and were<br>conscious in the cost<br>and use of resources |

| Property<br>Ownership         | Our definition of<br>property ownership is<br>making sure that our<br>project is properly being<br>used and that we are<br>properly handing our<br>project over once we<br>finish it                                      | <b>9.</b> To avoid injuring others, their property, reputation, or employment by false or malicious action                                                                                                                                                                                            | Our team has focused<br>on ensuring that our<br>project and deliverable<br>will persist long after<br>the end of this project<br>to serve as an<br>available educational<br>tool for future students                         |

| Sustainability                | Our definition of<br>sustainability is making<br>sure that we are not<br>misusing funds or<br>negatively affecting the<br>environment more than<br>needed (due to the<br>fabrication process)                             | 1. To accept responsibility<br>in making decisions<br>consistent with the safety,<br>health, and welfare of the<br>public, and to disclose<br>promptly factors that<br>might endanger the public<br>or the environment                                                                                | Our team focused on<br>ensuring that our<br>project is sustainable<br>by making it open<br>source as well as by<br>making this a resource<br>for students to use for<br>years to come                                        |

| Social<br>Responsibility | Our definition of<br>sustainability is making<br>sure that our project is<br>used to help others and<br>that everyone will be<br>able to use our project<br>no matter age, race,<br>gender, etc. | 2. to improve the<br>understanding by<br>individuals and society of<br>the capabilities and societal<br>implications of conventional<br>and emerging technologies,<br>including intelligent<br>systems; | We have as a team<br>troubleshooted at<br>every turn in our<br>project and done<br>research to make each<br>component open<br>source and picked IP<br>that is projected to be<br>supported well into the |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                                                                                                                                                                                                  |                                                                                                                                                                                                         | supported well into the future                                                                                                                                                                           |

Table 5: Code of Ethics

One area of responsibility we are doing well in is communication. We keep constant contact with each other and exchange information and progress frequently. Communication is the bedrock of a good team and is indicative of strong performance because efficient communication leads to good task delegation and progress.

One area of responsibility we could improve is social responsibility. Currently our project is very technical and difficult to learn from, this could be unfair to those with less resources and less experience. To address this, we can make sure our project has documentation that properly explains the technologies that are being used and provides resources for them to use.

# Four Principles

|                                          | Beneficence                                             | Nonmaleficence                                            | Respect for<br>Autonomy                                         | Justice                                                                 |

|------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------|

| Public health,<br>safety, and<br>welfare | Project adds to<br>the knowledge of<br>chip fabrication | Design does not<br>support unsafe or<br>harmful practices | This project is not<br>forced upon<br>anyone to use             | Project promotes<br>access to<br>hardware for<br>marginalized<br>groups |

| Global,<br>cultural,<br>and social       | This project helps<br>students learning<br>hardware     | The project will<br>not harm any<br>particular group      | Design respects<br>and does not<br>affect<br>cultural practices | Project hopes to<br>help and give<br>opportunities to<br>all people     |

| Environmental                            | Accelerator<br>reduces power<br>use                     | We make sure<br>that our design<br>isn't wasteful         | This project does<br>not produce or<br>force any waste          | This might help<br>reduce power<br>usage from Al                        |

| Economic                                 | Supports open-<br>source fabrication                    | Design would not<br>disrupt the<br>economy                | This project does<br>not force anyone<br>to purchase            | This would not<br>financially affect<br>a specific person               |

Table 6 6: Four Principles Table

One important broad context-principal pair for our project is Economic – Beneficence. We all want to contribute something to the knowledge of Computer Engineering and to contribute and support the open-source community, and our project is a good way to do both. We will ensure that our project remains open source to anyone that wishes to use it.

One broad context-principal pair that our project will be lacking in is environment and Nonmaleficence. We cannot ensure that our project isn't wasteful, someone could theoretically use the CyGRA in a way that is inefficient and therefore wasteful of power. However, we do think that the potential power that can be saved by an efficiently used CyGRA will outweigh the negatives for inefficient use.

## Virtues

Our team believes that the three most important virtues are Integrity, Communication, and Respect. Integrity to us means to upload honesty for the team no matter what as well as being transparent with both each other and our advisor and client to build trust and respect. Communication helps us ensure we are always in talks with each other about the project and where we are so everyone can get a good sense of progress. Respect means for us to be kind and understanding of others in the event of difficulties or other reasons and to always be understanding.

Camden:

### Virtue Demonstrated --- Communication

To support communication and trust I keep in contact with the team and lead team meetings to help foster a successful and friendly environment for the whole team, so everyone feels safe to talk about whatever they need, good or bad.

### Virtue Undemonstrated --- Self-discipline